I218 Computer Architecture

Report 3

计算机体系结构代做 Question 1(1) In the textbook and lecture slides, detailed information in the pipeline registers (IF/ID, ID/EX, EX/MEM, MEM/WB) is not provided.

Question 1 计算机体系结构代做

(1) In the textbook and lecture slides, detailed information in the pipeline registers (IF/ID, ID/EX, EX/MEM, MEM/WB) is not provided. Actually, each pipeline register can be divided into several fields. For “EX/MEM” pipeline register, give a name to each field, show the bit-width of it, and explain the role of it (including the fields for each control signal). Suppose the datapath/organization follows Figure 4.51 in Lec5_e.pdf, 6th slide. (1 pt. for all)

Ex.) As for “IF/ID” pipeline register,

NPC (32 bits): next PC (PC+4)

IR (32 bits): instruction itself

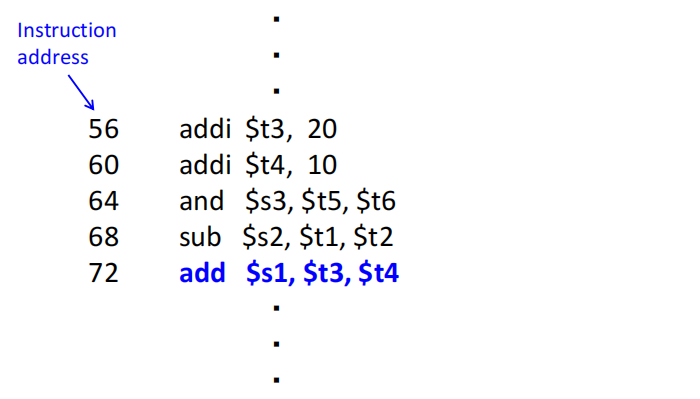

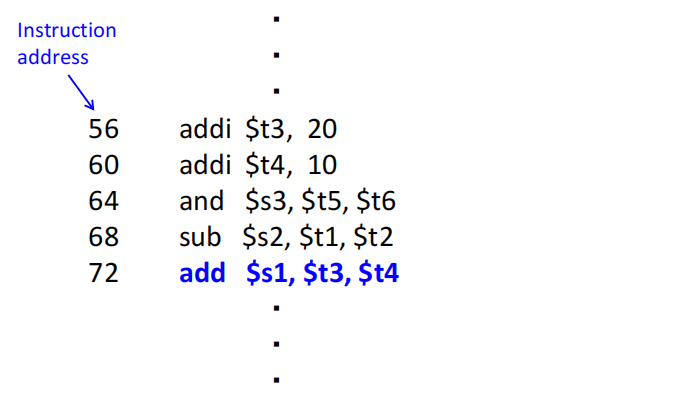

(2) Answer the binary value of each field (you defined in (1)) in EX/MEM pipeline register when the “add” instruction in the following code exists in MEM stage. (1 pt. for all)

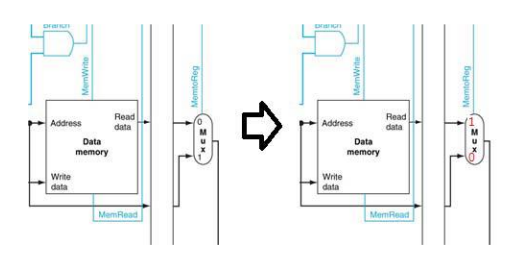

- In Figure 4.51, the multiplexor with “MemtoReg” includes a mistake.

– MemtoReg has to be “1” when data read from Data memory is selected.

(3) What is “delayed branch” ? The answer must include the aim and the mechanism. (1 pt.)

Question 2 计算机体系结构代做

The following code has loop structure. (Delayed branch is assumed.)

Loop: lw $t0, 512 ($s3) lw $t1, 0 ($s3) add $t2, $t0, $t1 addi $t2, $t2, 4 sw $t2, 2048 ($s3) bne $s3, $s2, Loop addi $s3, $s3, 4 # delay slot

(1) If the instruction sequence is executed by the MIPS 5-stage, single issue pipeline, what is CPI ? Basically, it is supposed that one instruction takes 1-cycle to execute, except that data hazards by load instructions generate 1-cycle bubble. (0.5 pt.)

(2) If the code sequence is restructured (without code scheduling) and executed by the MIPS static multiple issue (2 instructions issue), what is CPI ? Show a table like one in the 7th lecture slide(Lec7_e.pdf), page 6. (Both CPI value and the table are required.) (0.5 pt.)

(3) Apply code scheduling to the code sequence derived in (2) in order to decrease CPI. Show a code (table) after code scheduling, and CPI. (Both CPI value and the table are required.) (0.5 pt.)

(4) Apply loop unrolling (so that 4 iterations are packed into a loop body) and code scheduling with register renaming in order to obtain smaller CPI. Show a code (table) after unrolling and code scheduling, and CPI. (Both CPI value and the table are required.) (0.5 pt.)

Caution

- A copy from others can’t be accepted.

- A duplicate answer gets zero point even if it is the original answer.

更多代写:R语言代写 宗教学代考 英国物理网课代修 影视类essay代写 英语研究论文Research Paper代写 AI人工智能代写