I218E Computer Architecture Midterm Examination

I218E代写 (1) Given the increase in “Die area” of DRAMs, what parameter in the above equations must improve to maintain yield?

Problem 1

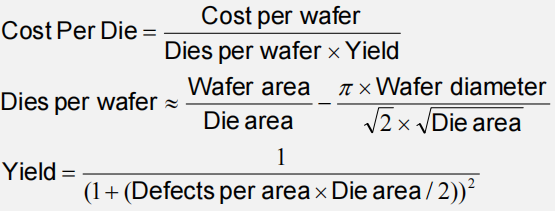

The cost of an integrated circuit can be expressed in the following equations:

| Year | Capacity(Kbits) | Die area (cm2) | Wafer diameter (cm) | Yield |

| 1980 | 64 | 0.18 | 12.6 | 46% |

| 1983 | 256 | 0.22 | 12.8 | 45% |

| 1985 | 1,024 | 0.40 | 15.2 | 48% |

| … | … | … | … | … |

| 2018 | 4,194,304 | 0.78 | 32.0 | 46% |

(1) Given the increase in “Die area” of DRAMs, what parameter in the above equations must improve to maintain yield? (3 pt.)

_________________________________

(2) Derive a formula for the parameter found in(1)from the other parameters (i.e., by deformation). (2 pt.)

_________________________________

(3) Using the formula in the answer to(2), what is the calculated improvement in that parameter between 1980 and 2016 ? (Calculation process is required.) (2 pt.)

_________________________________

Problem 2 I218E代写

(1) Execution of some program on a computer A with CPU of 1.5 GHz takes 10 seconds. We want to build a new computer B that can run this program in 8 seconds. If the computer B requires 1.6 times as many clock cycles as the computer A for this program, what clock rate should be achieved ? (Calculation process is required.) (2 pt.)

(2) Explain “CPI” and “IPC” as performance criteria? (3 pt.)

(3) What is “Amdahl’s Law” ? Answer it briefly. (3 pt.)

Problem 3 I218E代写

Consider two different implementations, M1 and M2, of the same instruction set. There are four classes of instructions (A, B, C, and D) in this instruction set.

| Instruction class | CPI | Frequency |

| A | 1 | 40% |

| B | 2 | 35% |

| C | 3 | 15% |

| D | 4 | 10% |

M1 has a clock rate of 2000 MHz (=2.0GHz). The average number of cycles for each instruction class (CPI) of M1 and frequency (usage) of each instruction class of some program X are as follows.

| Instruction class | CPI | Frequency |

| A | 2 | 40% |

| B | 2 | 35% |

| C | 4 | 15% |

| D | 4 | 10% |

M2 has a clock rate of 3000 MHz (=3.0GHz). The average number of cycles for each instruction class (CPI) of M2 and frequency of each instruction class of the (same) program X are as follows.

Answer the following questions.

(1) Calculate CPIs when the program X is executed by M1 and M2, respectively ? (3 pt.)

(2) How much faster is M2 than M1 for the program X ? (Calc. process is required.) (3 pt.)

Problem 4

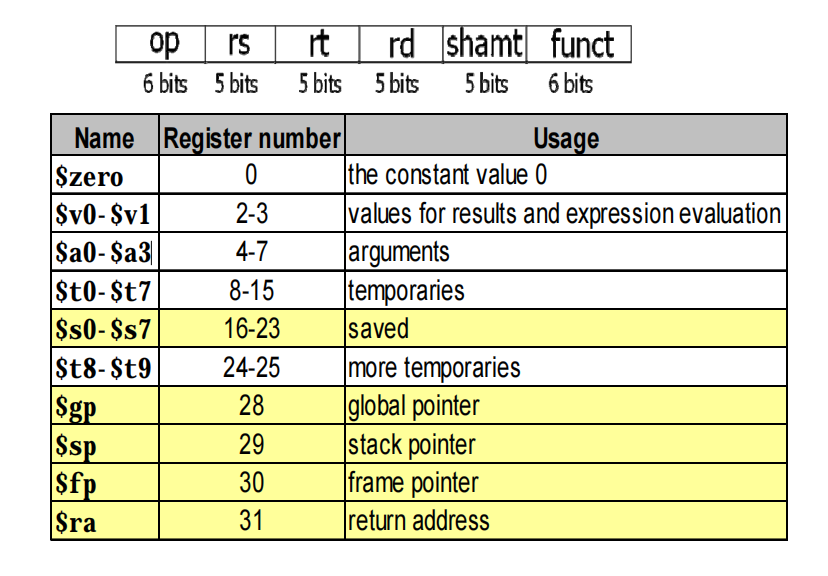

(1) How is the instruction “and $t9, $s2, $t5” translated to a machine instruction code? Answer the rs, rt, and rd fields in binary number. (1 pt. for each)

For “and $t9, $s2, $t5”

rs =__________ rt =________ rd =_________

(2) Fill the blanks (A) to (D) in the following code sequence which calculates “A[260] = h + A[4]”. The array “A” consists of 4-byte integer elements. Assume that $s2 and $s3 are allocated to “h” and the base address of “A”, respectively. (1 pt. for each)

lw (A) , (B) ($s3)

add (C) , $s2, $t1

sw $t0, (D) ($s3)

(A) ______ (B) ______ (C) ______ (D) ______

Problem 5

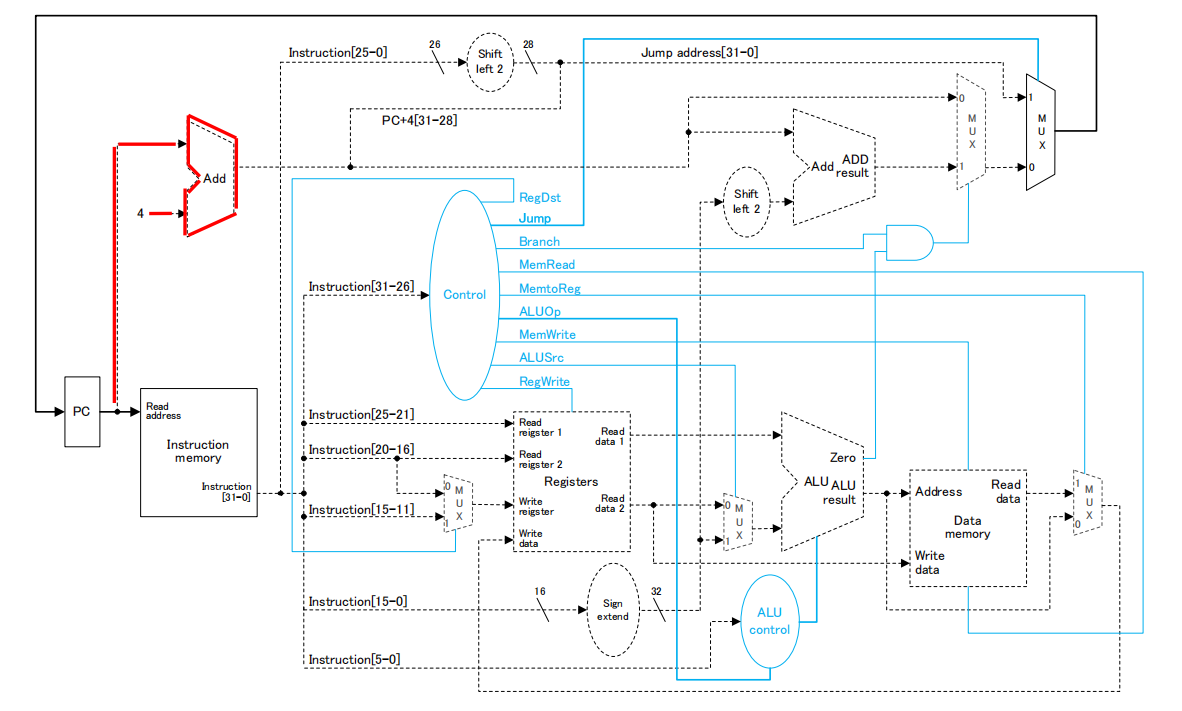

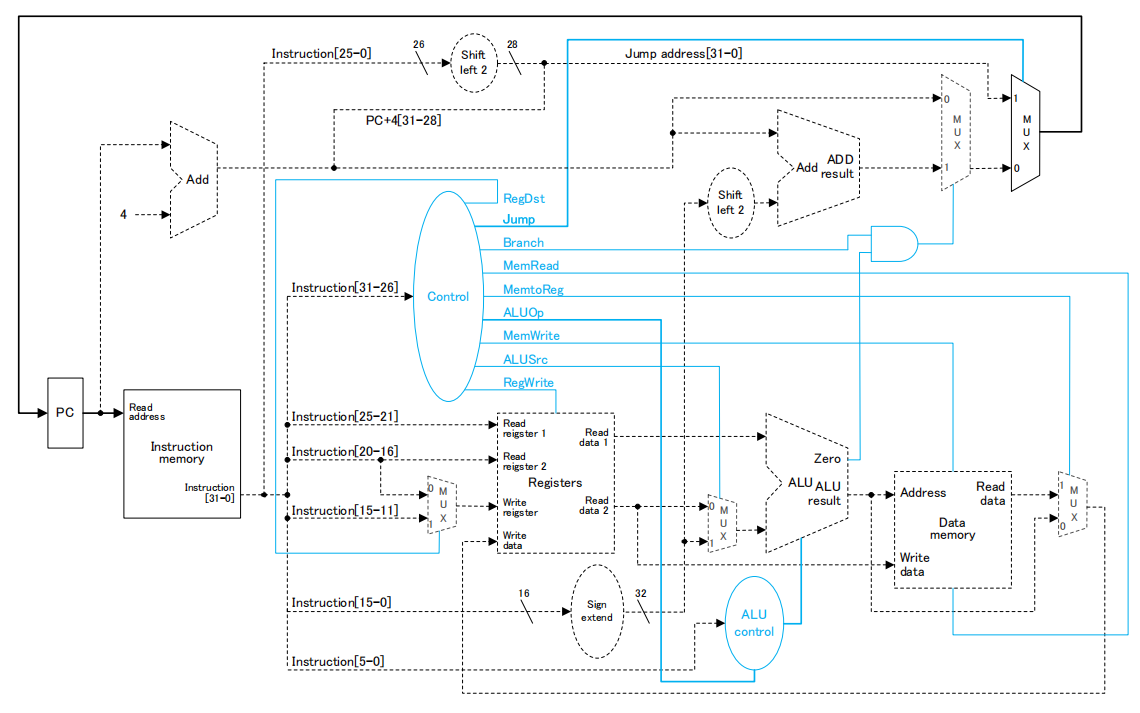

This problem is for a processor of MIPS single-cycle implementation.

(1)Highlight the components and lines which are related to (meaningful for) the execution of “add”. (Highlight by tracing dotted lines with solid lines like red lines in the figure. Ignore the blue (control) lines.) (3 pt.)

(2)Highlight the components and lines which are related to the execution of “lw”. (Ignore the blue (control) lines.) (3 pt)

(3)Among “add”, “beq”, “lw”, “sw” and “j”, which instruction generates the longest delay (requires the longest time) in the execution? Answer with the reason. (2 pt)

Problem 6 I218E代写

(1) Enumerate the names of the five stages of the MIPS pipelining in the lecture and the textbook. (2 pt. for all)

(2) Describe the role of “pipeline registers.” (2 pt.)

其他代写:CS代写 Data Analysis代写 data代写 澳大利亚代写 essay代写 assignment代写 analysis代写 code代写 assembly代写 homework代写 Exercise代写 加拿大代写 英国代写 作业代写 app代写 algorithm代写 作业加急 北美代写 北美作业代写

合作平台:essay代写 论文代写 写手招聘 英国留学生代写